# **Advantech**

# AQD-D5V32GN56-SB Datasheet

Rev. 1.0 2024-05-23

## **ADVANTECH**

**Enabling an Intelligent Planet**

#### 288Pin DDR5 5600 1.1V U-DIMM 32GB Based on 2048Mx8 AQD-D5V32GN56-SB

#### Description

AQD-D5V32GN56-SB is DDR5-5600(CL46)-45-45 SDRAM memory module. The SPD is programmed to JEDEC standard latency 5600Mbps timing of 46-45-45 at 1.1V. The module is composed of 16Gb CMOS DDR5 SDRAMs in FBGA package and one 8Kbit SPD Hub in 8pin TDFN package on a 288pin glass–epoxy printed circuit board.

The module is a Dual In-line Memory Module and intended for mounting onto 288 pins edge connector sockets. Synchronous design allows precise cycle control with the use of system clock. Data I/O transactions are possible on both edges of DQS. Range of operating frequencies, programmable latencies and burst lengths allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

#### Features

- RoHS compliant products.

- JEDEC standard 1.1V(1.067V~1.166V) Power supply

- VDDQ= 1.1V(1.067V~1.166V)

- VPP = 1.8V(+0.108V / -0.054V)

- Data transfer rates: PC5-5600

- Programmable CAS Latency: 22,26,28,30,32,36,40,42,46

- 16 bit pre-fetch

- Burst Length (BL) switch on-the-fly BL16 or BC8

- Bi-directional Differential Data-Strobe

- On Die Termination, Nominal, Park

- Serial presence detect hub (SPD Hub) with

Integrated Temperature sensor

- Asynchronous reset

- PCB edge connector treated with 30u" Gold-Plating

| Pin Name               | Description                                | Pin Name                       | Description                                               |

|------------------------|--------------------------------------------|--------------------------------|-----------------------------------------------------------|

| CA[6:0]_A<br>CA[6:0]_B | Address and Command Bus                    | DQ[31:0]_A<br>DQ[31:0]_B       | DIMM memory Data bus channel A & B                        |

| CS[1:0]_A<br>CS[1:0]_B | Chip Select                                | CB[7:0]_A<br>CB[7:0]_B         | DIMM ECC Checkbits (CB) channel A & B                     |

| PAR_A<br>PAR_B         | Parity input                               | DQS[9:0]_A_t<br>DQS[9:0]_B_t   | Data Strobes<br>(positive line of differential pair)      |

| CK_t                   | Clocks (true/positive)                     | DQS[9:0]_A_c<br>DQS[9:0]_B_c   | Data Strobes<br>(negative line of differential pair)      |

| CK_c                   | Clocks (complement/negative)               | TDQS[9:5]_A_t<br>TDQS[9:5]_B_t | Not valid for x4 operation. Enabled via<br>Mode Register. |

| ALERT_n                | Alert for CRC error                        | TDQS[9:5]_A_c<br>TDQS[9:5]_B_c | Not valid for x4 operation. Enabled via<br>Mode Register. |

| RESET_n                | Set DRAM to known state                    | VIN_BULK                       | DIMM Power Supply from system to PMIC                     |

| PCAMP                  | Control and Monitor Port                   | VIN_MGMT                       | DIMM Power Supply from system to PMIC                     |

| HSCL                   | I2C/I3C-Basic Host Sideband Bus<br>Clock   | VSS                            | Power supply return (ground)                              |

| HSDA                   | I2C/I3C-Basic Host Sideband Bus Data       | RFU                            | Reserved for future use                                   |

| HSA                    | I2C/I3C-Basic Host Sideband Bus<br>Address | LBDQS                          | Loopback Data strobe output                               |

| LBDQ                   | Loopback Data output:                      |                                |                                                           |

#### 3

#### **Dimensions (Unit: millimeter)** Fron Pub Hub PMIC Back 133.35+0.45 5250+18 5.57 MAX 3.875 [153] 31.25<sup>+0.55</sup> [ 1230<sup>+22<sup>-</sup></sup> R0.80 [R31](2X) Hole [Ø59](4X) A В D 1.27±0.10 [50±4] nganananan (mi [6 VIEW E-E [2476] 57.80 [2276] 3.35 [132] 5.95 [234] 3.35 [132] 133.35 <u>36.08 [1420]</u> 9.35 [368] 30.22 [1190] 22.48 [885] 24.38 [960] 9.35 [368] 30 [1272] <u>8.50 [335</u> 28.90 [1138] 0.40 [803] 8.50 [335] 18 70 8.00 [315](2X) R0.65 [R263(8X) 3.00 [118](4X) 2.10 [83](4X) [575](2X) 4.60 0.60±0.03 [24±1] 3.85±0.10 [152±4] ω 2.10 0.85 [33] הההחחו 4.30 [169] 0.25 [10] 1.65 [65] 0.20 [8] 1.50±0.05 [59±2] Detail A Detail B 2.60 [102] [83] [83] Pin122 <u>2.10</u> Pin39 'in110 2.10 Pin51

Note:1. Tolerances on all dimensions +/-0.15mm unless otherwise specified.

0.25

2.60

С

Detail

0.25 [10]

0.50 [20]

Detail D

0.25 [10]

0.50 [2

## 288Pin DDR5 5600 1.1V U-DIMM 32GB Based on 2048Mx8 AQD-D5V32GN56-SB

#### **Pin Assignments**

|     |                 | 2   | 88-Pin DDR5 | UDIN | AM Front |     |                 | 288-Pin DDR5 UDIMM Back |                 |     |                 |     |                 |     |                 |

|-----|-----------------|-----|-------------|------|----------|-----|-----------------|-------------------------|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| Pin | Symbol          | Pin | Symbol      | Pin  | Symbol   | Pin | Symbol          | Pin                     | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

| 1   | VIN_BULK        | 37  | DQ20_A      | 73   | CK0_A_c  | 109 | V <sub>SS</sub> | 145                     | VIN_BULK        | 181 | DQ22_A          | 217 | CK1_A_c         | 253 | Vss             |

| 2   | NC/VIN_BULK     | 38  | Vss         | 74   | Vss      | 110 | DQ5_B           | 146                     | VIN_BULK        | 182 | Vss             | 218 | Vss             | 254 | DQ7_B           |

| 3   | RFU             | 39  | DQ21_A      | 75   | RFU      | 111 | V <sub>SS</sub> | 147                     | PWR_GOO<br>D    | 183 | DQ23_A          | 219 | RFU             | 255 | V <sub>SS</sub> |

| 4   | HSCL            | 40  | Vss         | 76   | RFU      | 112 | DQ8_B           | 148                     | HSA             | 184 | Vss             | 220 | RFU             | 256 | DQ10_B          |

| 5   | HSDA            | 41  | DQ24_A      | 77   | Vss      | 113 | V <sub>SS</sub> | 149                     | RFU             | 185 | DQ26_A          | 221 | V <sub>SS</sub> | 257 | Vss             |

| 6   | Vss             | 42  | Vss         | 78   | CK0_B_t  | 114 | DQ9_B           | 150                     | Vss             | 186 | Vss             | 222 | CK1_B_t         | 258 | DQ11_B          |

| 7   | RFU             | 43  | DQ25_A      | 79   | CK0_B_c  | 115 | Vss             | 151                     | PWR_EN          | 187 | DQ27_A          | 223 | CK1_B_c         | 259 | Vss             |

| 8   | Vss             | 44  | Vss         | 80   | Vss      | 116 | DM1_B_n         | 152                     | RFU             | 188 | Vss             | 224 | Vss             | 260 | DQS1_B_c        |

| 9   | DQ0_A           | 45  | DM3_A_n     | 81   | RFU      | 117 | Vss             | 153                     | Vss             | 189 | DQS3_A_c        | 225 | RFU             | 261 | DQS1_B_t        |

| 10  | Vss             | 46  | Vss         | 82   | CA12_B   | 118 | DQ12_B          | 154                     | DQ2_A           | 190 | DQS3_A_t        | 226 | RFU             | 262 | Vss             |

| 11  | DQ1_A           | 47  | DQ28_A      | 83   | Vss      | 119 | Vss             | 155                     | Vss             | 191 | Vss             | 227 | Vss             | 263 | DQ14_B          |

| 12  | Vss             | 48  | Vss         | 84   | CA10_B   | 120 | DQ13_B          | 156                     | DQ3_A           | 192 | DQ30_A          | 228 | CA11_B          | 264 | Vss             |

| 13  | DQS0_A_c        | 49  | DQ29_A      | 85   | CA8_B    | 121 | VSS             | 157                     | V <sub>SS</sub> | 193 | V <sub>SS</sub> | 229 | CA9_B           | 265 | DQ15_B          |

| 14  | DQS0_A_t        | 50  | Vss         | 86   | Vss      | 122 | DQ16_B          | 158                     | DM0_A_n         | 194 | DQ31_A          | 230 | Vss             | 266 | Vss             |

| 15  | Vss             | 51  | CB0_A       | 87   | CA6_B    | 123 | V <sub>SS</sub> | 159                     | V <sub>SS</sub> | 195 | V <sub>SS</sub> | 231 | CA7_B           | 267 | DQ18_B          |

| 16  | DQ4_A           | 52  | Vss         | 88   | CA4_B    | 124 | DQ17_B          | 160                     | DQ6_A           | 196 | CB2_A           | 232 | CA5_B           | 268 | Vss             |

| 17  | Vss             | 53  | CB1_A       | 89   | Vss      | 125 | V <sub>SS</sub> | 161                     | V <sub>SS</sub> | 197 | V <sub>SS</sub> | 233 | V <sub>SS</sub> | 269 | DQ19_B          |

| 18  | DQ5_A           | 54  | Vss         | 90   | CA2_B    | 126 | DQS2_B_c        | 162                     | DQ7_A           | 198 | CB3_A           | 234 | CA3_B           | 270 | Vss             |

| 19  | Vss             | 55  | DQS4_A_c    | 91   | CA0_B    | 127 | DQS2_B_t        | 163                     | Vss             | 199 | Vss             | 235 | CA1_B           | 271 | DM2_B_n         |

| 20  | DQ8_A           | 56  | DQS4_A_t    | 92   | Vss      | 128 | Vss             | 164                     | DQ10_A          | 200 | ALERT_n         | 236 | Vss             | 272 | Vss             |

| 21  | Vss             | 57  | Vss         | 93   | CS0_B_n  | 129 | DQ20_B          | 165                     | Vss             | 201 | Vss             | 237 | CS1_B_n         | 273 | DQ22_B          |

| 22  | DQ9_A           | 58  | CS0_A_n     | 94   | Vss      | 130 | VSS             | 166                     | DQ11_A          | 202 | CS1_A_n         | 238 | Vss             | 274 | Vss             |

| 23  | Vss             | 59  | Vss         | 95   | RESET_n  | 131 | DQ21_B          | 167                     | Vss             | 203 | Vss             | 239 | DQS4_B_c        | 275 | DQ23_B          |

| 24  | DM1_A_n         | 60  | CA0_A       | 96   | Vss      | 132 | V <sub>SS</sub> | 168                     | DQS1_A_c        | 204 | CA1_A           | 240 | DQS4_B_t        | 276 | Vss             |

| 25  | Vss             | 61  | CA2_A       | 97   | CB0_B    | 133 | DQ24_B          | 169                     | DQS1_A_t        | 205 | CA3_A           | 241 | Vss             | 277 | DQ26_B          |

| 26  | DQ12_A          | 62  | Vss         | 98   | Vss      | 134 | V <sub>SS</sub> | 170                     | Vss             | 206 | V <sub>SS</sub> | 242 | CB2_B           | 278 | Vss             |

| 27  | V <sub>SS</sub> | 63  | CA4_A       | 99   | CB1_B    | 135 | DQ25_B          | 171                     | DQ14_A          | 207 | CA5_A           | 243 | Vss             | 279 | DQ27_B          |

| 28  | DQ13_A          | 64  | CA6_A       | 100  | Vss      | 136 | Vss             | 172                     | Vss             | 208 | CA7_A           | 244 | CB3_B           | 280 | Vss             |

| 29  | Vss             | 65  | Vss         | 101  | DQ0_B    | 137 | DM3_B_n         | 173                     | DQ15_A          | 209 | Vss             | 245 | V <sub>SS</sub> | 281 | DQS3_B_c        |

| 30  | DQ16_A          | 66  | CA8_A       | 102  | Vss      | 138 | Vss             | 174                     | Vss             | 210 | CA9_A           | 246 | DQ2_B           | 282 | DQS3_B_t        |

| 31  | V <sub>SS</sub> | 67  | CA10_A      | 103  | DQ1_B    | 139 | DQ28_B          | 175                     | DQ18_A          | 211 | CA11_A          | 247 | V <sub>SS</sub> | 283 | Vss             |

| 32  | DQ17_A          | 68  | Vss         | 104  | Vss      | 140 | Vss             | 176                     | Vss             | 212 | Vss             | 248 | DQ3_B           | 284 | DQ30_B          |

| 33  | Vss             | 69  | CA12_A      | 105  | DQS0_B_c | 141 | DQ29_B          | 177                     | DQ19_A          | 213 | RFU             | 249 | Vss             | 285 | Vss             |

| 34  | DQS2_A_c        | 70  | RFU         | 106  | DQS0_B_t | 142 | Vss             | 178                     | Vss             | 214 | RFU             | 250 | DM0_B_n         | 286 | DQ31_B          |

| 35  | DQS2_A_t        | 71  | Vss         | 107  | Vss      | 143 | RFU             | 179                     | DM2_A_n         | 215 | Vss             | 251 | Vss             | 287 | Vss             |

| 36  | Vss             | 72  | CK0_A_t     | 108  | DQ4_B    | 144 | RFU             | 180                     | Vss             | 216 | CK1_A_t         | 252 | DQ6_B           | 288 | RFU             |

#### Notes:

Pin #2 is NC (No Connect) for JEDEC standard DDR5 modules. On non-standard modules used by enthusiasts that may require increased power supply, Pin #2 can be connected to VIN\_BULK rail on module.

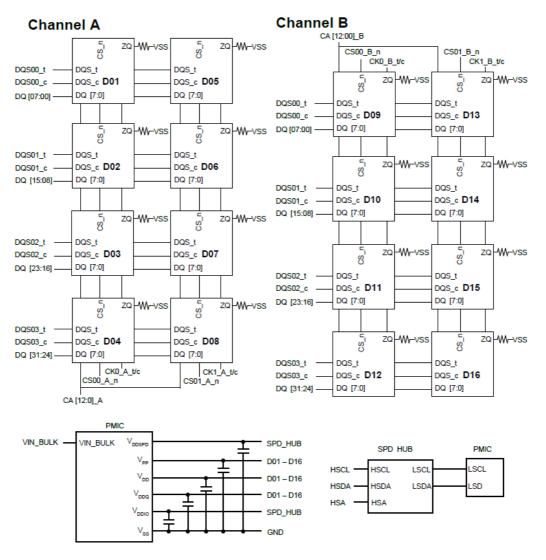

#### **Function Block Diagram**

#### 2Rank, x8 DDR5 SDRAMs

Note 1: ZQ resistors are 240  $\Omega \pm 1\%$ .

This technical information is based on industry standard data and tests believed to be reliable. However, Advantech makes no warranties, either expressed or implied, as to its accuracy and assume no liability in connection with the use of this product. Advantech reserves the right to make changes in specifications at any time without prior notice.

#### 288Pin DDR5 5600 1.1V U-DIMM 32GB Based on 2048Mx8 AQD-D5V32GN56-SB

#### Operating Temperature Condition

|        | Parameter                                                                                                                         | Symbol        | Rating     | Unit    | Note |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|------------|---------|------|

| Operat | ing Temperature                                                                                                                   | TOPER         | 0 to 85    | °C      | 1,2  |

| Note:  | Operating Temperature is the case surface temperature on the center/to measurement conditions, please refer to JESD51-2 standard. | op side of th | ne DRAM. I | For the |      |

#### **Absolute Maximum DC Ratings**

| Parameter                           | Symbol    | Value      | Unit | Note |

|-------------------------------------|-----------|------------|------|------|

| Voltage on VDD relative to Vss      | VDD       | -0.3 ~ 1.4 | V    | 1    |

| Voltage on VDDQ pin relative to Vss | VDDQ      | -0.3 ~ 1.4 | V    | 1    |

| Voltage on any pin relative to Vss  | VIN, VOUT | -0.3 ~ 1.4 | V    | 1    |

| Storage temperature                 | TSTG      | -55~+100   | °C   | 1,2  |

Note: 1. Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

#### AC & DC Operating Conditions

#### **Recommended DC operating conditions**

| Parameter                  | Symphol  | Voltage        |       | l lmit | Notes |      |       |

|----------------------------|----------|----------------|-------|--------|-------|------|-------|

| Farameter                  | Symbol   | Symbol Voltage |       | Тур.   | Мах   | Unit | Notes |

| Host Supply Voltage        | VIN_BULK | 12.0           | 4.25  | 5.0    | 5.5   | V    |       |

| PMIC Output Supply Voltage | VDD      | 1.1            | 1.067 | 1.1    | 1.166 | V    | 1,2,3 |

| PMIC Output Supply Voltage | VDDQ     | 1.1            | 1.067 | 1.1    | 1.166 | V    | 1,2,3 |

| PMIC Output Supply Voltage | VPP      | 1.8            | 1.746 | 1.8    | 1,908 | V    | 3     |

| AC Input Logic High        | VIH(AC)  | TBD            | -     | -      | -     | mV   |       |

| AC Input Logic Low         | VIL(AC)  | TBD            | -     | -      | -     | mV   |       |

| DC Input Logic High        | VIH(DC)  | TBD            | -     | -      | -     | mV   |       |

| DC Input Logic Low         | VIL(DC)  | TBD            | -     | -      | -     | mV   |       |

Note: (1) VDD must be within 66mv of VDDQ

(2) AC parameters are measured with VDD and VDDQ tied together.

(3) This includes all voltage noise from DC to 2 MHz at the DRAM package ball.

## IDD Specification parameters Definition - 32GB

| Symbol | Condition                                               | 32GB | Unit |

|--------|---------------------------------------------------------|------|------|

| IDD0   | One bank ACTIVATE-PRECHARGE current                     | TBD  | mA   |

| IDD0F  | Operating Four Bank Active-Precharge Current            | TBD  | mA   |

| IDD2N  | Precharge Standby Current                               | TBD  | mA   |

| IDD2P  | Precharge Power-Down Current                            | TBD  | mA   |

| IDD3N  | Active standby current                                  | TBD  | mA   |

| IDD3P  | Active Power-Down Current                               | TBD  | mA   |

| IDD4R  | Burst Read Current                                      | TBD  | mA   |

| IDD4W  | Burst write current                                     | TBD  | mA   |

| IDD5B  | Burst Refresh Current (1x REF)                          | TBD  | mA   |

| IDD5C  | Burst Refresh Current (Same Bank Refresh Mode)          | TBD  | mA   |

| IDD6N  | Self refresh current: Normal temperature range (0–85°C) | TBD  | mA   |

| IDD7   | Bank interleave read current                            | TBD  | mA   |

| IDD8   | Maximum power-down current                              | TBD  | mA   |

| Timing Param                                                                 | eters & Sp | ecificatio          | ons            |                                      |                  |                     |           |        |         |

|------------------------------------------------------------------------------|------------|---------------------|----------------|--------------------------------------|------------------|---------------------|-----------|--------|---------|

| _                                                                            |            | DDR5                | -4800          | DDR5                                 | -5600            | DDR5                | DDR5-6400 |        |         |

| Parameter                                                                    | Symbol     | Min                 | Мах            | Min                                  | Мах              | Min                 | Мах       | Unit   | Notes   |

|                                                                              |            |                     | Clock          | Timing                               |                  |                     |           |        |         |

| Clock period average                                                         | tCK (AVG)  | 0.416               | <0.454         | 0.357                                | <0.384           | 0.312               | <0.333    | ns     | 1       |

| Command and Address Timing                                                   |            |                     |                |                                      |                  |                     |           |        |         |

| Read to Read command delay<br>for same bank group                            | tCCD_L     | max(8nCK,<br>5ns)   | _              | max(8nCK,<br>5ns)                    | -                | max(8nCK,<br>5ns)   | -         | nCK,ns | 8       |

| Write to Write command delay<br>for same bank groupp                         | tCCD_L_WR  | max(32nCK,<br>20ns) | _              | max(32nCK,<br>20ns)                  | _                | max(32nCK,<br>20ns) | _         | nCK,ns | 8       |

| Write to Write command delay<br>for same bank group, second<br>write not RMW | tCCD_L_WR2 | max(16nCK,<br>10ns) | _              | max(16nCK,<br>10ns)                  | _                | max(16nCK,<br>10ns) | _         | nCK,ns | 8       |

| Read to Write command delay<br>for same bank group                           | tCCD_L_RTW |                     | CL - CV        | /L + RBL/2 + 2tC<br>+ (tRPST - 0.5td |                  | S offset)           |           | nCK,ns | 3,5,6,8 |

| Write to Read command delay<br>for same bank group                           | tCCD_L_WTR |                     | C              | WL + WBL/2 + M                       | ax(16nCK,10n     | 5)                  |           | nCK,ns | 4,6,8   |

| Read to Read command delay<br>for different bank group                       | tCCD_S     | 8                   | -              | 8                                    | -                | 8                   | -         | nCK    | 8       |

| Write to Write command delay<br>for different bank group                     | tCCD_S_WR  | 8                   | _              | 8                                    | _                | 8                   | _         | nCK    | 8       |

| Read to Write command delay<br>for different bank group                      | tCCD_S_RTW | CL - CV             | VL + RBL/2 + 2 | tCK - (Read DQS                      | S offset) + (tRP | ST - 0.5tCK) + t    | WPRE      | nCK,ns | 3,5,6,8 |

| Write to Read command delay<br>for different bank group                      | tCCD_S_WTR |                     | С              | WL + WBL/2 + N                       | lax(4nCK,2.5ns   | 3)                  |           | nCK,ns | 4,6,8   |

| Write to Read with Auto<br>Precharge command delay for<br>same bank          | tCCD_WTRA  |                     |                | CWL + WBL/2 ·                        | + tWR - tRTP     |                     |           | nCK,ns | 2,4,6,8 |

|                                                                                    |            | DDR5-4800               |     | DDR5-5600               |   | DDR5-6400               |     |        |       |  |

|------------------------------------------------------------------------------------|------------|-------------------------|-----|-------------------------|---|-------------------------|-----|--------|-------|--|

| Parameter                                                                          | Symbol     | Min                     | Max | Min Max                 |   | Min                     | Max | Unit   | Notes |  |

| Activate to Activate command<br>delay to same bank group for<br>1KB page size      | tRRD_L(1K) | max(8nCK,<br>5ns)       | _   | max(8nCK,<br>5ns)       | _ | max(8nCK,<br>5ns)       | _   | nCK,ns | 8     |  |

| Activate to Activate command<br>delay to same bank group for<br>2KB page size      | tRRD_L(2K) | max(8nCK,<br>5ns)       | _   | max(8nCK,<br>5ns)       | _ | max(8nCK,<br>5ns)       | _   | nCK,ns | 8     |  |

| Activate to Activate command<br>delay to different bank group for<br>1KB page size | tRRD_S(1K) | 8                       | _   | 8                       | _ | 8                       | _   | nCK    | 8     |  |

| Activate to Activate command<br>delay to different bank group for<br>2KB page size | tRRD_S(2K) | 8                       | _   | 8                       | _ | 8                       | _   | nCK    | 8     |  |

| Four activate window for 1KB page size                                             | tFAW (1K)  | Max(32nCK,<br>13.333ns) | -   | Max(32nCK,<br>11.428ns) | - | Max(32nCK,<br>10.000ns) | -   | nCK,ns |       |  |

| Four activate window for 2KB page size                                             | tFAW (2K)  | Max(40nCK,<br>16.666ns) | _   | Max(40nCK,<br>14.285ns) | _ | Max(40nCK,<br>12.500ns) | -   | nCK,ns |       |  |

| Read to Precharge command delay                                                    | tRTP       | Max(12nCK,<br>7.5ns)    | _   | Max(12nCK,<br>7.5ns)    | _ | Max(12nCK,<br>7.5ns)    | _   | nCK,ns | 8     |  |

| Precharge to Precharge command delay                                               | tPPD       | 2                       | -   | 2                       | - | 2                       | -   | nCK    | 7,8   |  |

| Write recovery time                                                                | tWR        | 30                      | -   | 30                      | - | 30                      | -   | ns     | 8     |  |

#### Notes:

- 1. tCK(avg)min listed for reference only, refer to the Speed Bins and Operations section which lists all valid tCK(avg) values.

- 2. tCCD\_WTRA(min) shall always be greater than or equal to CWL + WBL/2 + tWR(min) tRTP(min), and when using the appropriate rounding algorithms,

nCCD\_WTRA(min) shall always be greater than or equal to CWL + WBL/2 + nWR(min) - nRTP(min).

- 3. RBL: Read burst length associated with Read command

- RBL = 32 (36 w/ RCRC on) for fixed BL32 and BL32 in BL32 OTF mode

- RBL = 16 (18 w/ RCRC on) for fixed BL16 and BL16 in BL32 OTF mode

- RBL = 16 (18 w/ RCRC on) for BL16 in BC8 OTF mode and BC8 in BC8 OTF mode

4. WBL: Write burst length associated with Write command

WBL = 32 (36 w/ WCRC on) for fixed BL32 and BL32 in BL32 OTF mode

WBL = 16 (18 w/ WCRC on) for fixed BL16 and BL16 in BL32 OTF mode

WBL = 16 (18 w/ WCRC on) for BL16 in BC8 OTF mode and BC8 in BC8 OTF mode

5.5 - The following is considered for tRTW equation

1tCK needs to be added due to tDQS2CK

Read DQS offset timing can pull in the tRTW timing

1tCK needs to be added when 1.5tCK postamble

- 6. CWL=CL-2

- 7. tPPD applies to any combination of precharge commands (PREab, PREsb, PREpb). tPPD also applies to any combination of precharge commands to a different die in a

3DS DDR5 SDRAM.

8. This parameter only specifies minimum values (there is no maximum value). The maximum value cells have been merged in

the table to improve legibility.

## 288Pin DDR5 5600 1.1V U-DIMM 32GB Based on 2048Mx8 AQD-D5V32GN56-SB

## SERIAL PRESENCE DETECT SPECIFICATION

| Byte | Function Described                                                                                         | -                                    | iction                      | HEX      |

|------|------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------|----------|

| 0 N  | umber of Bytes in SPD Device                                                                               | SPD Total                            | : 1024Bytes                 | r -      |

| 1 S  | PD Revision for Base Configuration Parameters                                                              | Vers                                 | ion 1.1                     |          |

| 2 K  | ey Byte / Host Bus Command Protocol Type                                                                   | DDR5                                 | SDRAM                       |          |

| 3 К  | ey Byte / Module Type                                                                                      |                                      | DIMM                        |          |

| 4 FI | rst SDRAM Density and Package                                                                              | Monolithic SDRAM                     | 16Gb                        |          |

| 5 FI | rst SDRAM Addressing                                                                                       | Row : 16                             | Column : 10                 |          |

| 6 FI | rst SDRAM I/O Width                                                                                        |                                      | x8                          |          |

| 7 FI | rst SDRAM Bank Groups & Banks Per Bank Group                                                               | 8 bank groups/4 b                    | anks per bank group         |          |

| 8 S  | econd SDRAM Density and Package                                                                            |                                      |                             |          |

| 9 S  | acond SDRAM Addressing                                                                                     |                                      |                             |          |

| 10 S | econdary SDRAM I/O Width                                                                                   |                                      |                             |          |

| 11 S | acond SDRAM Bank Groups & Banks Per Bank Group                                                             |                                      |                             |          |

| 12 S | DRAM BL32 & Post Package Repair                                                                            | One repair element per<br>bank group | Burst length 32 supported   |          |

| 3 S  | DRAM Duty Cycle Adjuster & Partial Array Self Refresh                                                      | Device supports DCA to               | r 4-phase internal clock(s) |          |

| 4 S  | DRAM Fault Handling                                                                                        |                                      | ision control in MR9        |          |

| _    | aserved a                                                                                                  |                                      | ded as 0x00                 |          |

| _    | DRAM Nominal Voltage, VDD                                                                                  | Operable:1.1V                        | Endurant:1.1V               |          |

| _    | DRAM Nominal Voltage, VDDQ                                                                                 | Operable:1.1V                        | Endurant:1.1V               |          |

|      | DRAM Nominal Voltage, VPP                                                                                  | Operable:1.8V                        | Endurant:1.8V               |          |

| _    | RAM Timing                                                                                                 |                                      | ings per JESD79-5           |          |

| _    | DRAM Minimum Cycle Time (tCKAVGmin), Least Significant Byte                                                | water name to be the UTI             | and the second second       |          |

|      | DRAM Minimum Cycle Time (CKAVGmin), Csart diginitari Cyte                                                  | 357                                  | 7 ps                        |          |

|      | DRAM Maximum Cycle Time (ICKAVGmax), Least Significant Byte                                                |                                      |                             | +        |

|      | DRAM Maximum Cycle Time (ICKAVGmax), Most Significant Byte                                                 | 1010                                 | ps (                        |          |

| _    | DRAM CAS Latencies Supported:First Byte                                                                    | 01.00.00                             | 5,28,30,32                  | +        |

| _    | DRAM CAS Latencies Supported:Second Byte                                                                   |                                      | 0,42,46,50                  | +        |

| -    |                                                                                                            | UL,30,41                             | 0,42,40,50                  |          |

| _    | DRAM CAS Latencies Supported:Third Byte                                                                    |                                      | •                           |          |

|      | DRAM CAS Latencies Supported Fourth Byte                                                                   |                                      |                             |          |

|      | DRAM CAS Latencies Supported Fifth Byte                                                                    |                                      | *                           | -        |

|      | eserved                                                                                                    | must be co                           | ded as 0x00                 | -        |

| _    | DRAM Minimum CAS Latency Time (tAAmin), Least Significant Byte                                             | 1600                                 | ) ps                        | <u> </u> |

| _    | DRAM Minimum CAS Latency Time (tAAmin), Most Significant Byte                                              |                                      |                             | -        |

| _    | DRAM Minimum RAS to CAS Delay Time (RCDmin), Least Significant Byte                                        | 1600                                 | ) ps                        |          |

| _    | DRAM Minimum RAS to CAS Delay Time (RCDmin), Most Significant Byte                                         |                                      |                             | -        |

| _    | DRAM Minimum Row Precharge Delay Time (tRPmin), Least Significant Byte                                     | 1600                                 | ) os                        |          |

| _    | DRAM Minimum Row Precharge Delay Time (IRPmin), Most Significant Byte                                      |                                      |                             | _        |

| _    | DRAM Minimum Active to Precharge Delay Time (IRASmin), Least Significant Nibble                            | 3200                                 | ) os                        |          |

|      | DRAM Minimum Active to Precharge Delay Time (RASmin), Most Significant Byte                                |                                      | - P.3                       |          |

| 8 S  | DRAM Minimum Active to Active/Refresh Delay Time (RCmin), Least Significant Nibble                         | 4800                                 | -                           |          |

| 9 S  | DRAM Minimum Active to Active/Refresh Delay Time (IRCmin), Most Significant Nibble                         | -000                                 | , pa                        |          |

| 0 S  | DRAM Minimum Write Recovery Time (tWRmin), Least Significant Nibble                                        | - 3000                               |                             |          |

| 1 S  | DRAM Minimum Write Recovery Time (tWRmin), Most Significant Nibble                                         | 3000                                 | - P.0                       |          |

| 2 S  | DRAM Minimum Refresh Recovery Delay Time (IRFC1 min, IRFC1 sir min).Least Significant Byte                 |                                      | 5 ns                        |          |

| 3 S  | DRAM Minimum Refresh Recovery Delay Time (IRFC1 min, IRFC1 sir min),Most Significant Byte                  | 230                                  | 112                         |          |

| 4 S  | DRAM Minimum Refresh Recovery Delay Time (IRFC2min, IRFC2 sir min),Least Significant Byte                  |                                      |                             |          |

| 5 S  | DRAM Minimum Refresh Recovery Delay Time (IRFC2min, IRFC2 sir min),Most Significant Byte                   | 160                                  | ) ns                        |          |

|      | DRAM Minimum Refresh Recovery Delay Time (IRFCsbmin, IRFCsb sir min)Least Significant Byte                 |                                      |                             |          |

|      | DRAM Minimum Refresh Recovery Delay Time (IRFCsbmin, IRFCsb sirmin).Most Significant Byte                  | 130                                  | ) ns                        |          |

| _    | DRAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(RFC1 dir min) Least Significant Byte  |                                      |                             |          |

|      | DRAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(RFC1 dir min),Most Significant Byte   | manalithi                            | c SDRAMs                    |          |

| _    | DRAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(tRFC2 dir min)Least Significant Byte  |                                      |                             |          |

| _    | DRAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(RRC2 dir min).Most Significant Byte   | manalithi                            | c SDRAMs                    |          |

|      | ORAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(RRCsb dir min) Least Significant Byte |                                      |                             |          |

| _    | DRAM Minimum Refresh Recovery Delay Time, 3DS Different Logical Rank(RFCsb dir min),Most Significant Byte  | monolithi                            | c SDRAMs                    |          |

| _    | DRAM Refresh Management, First Byte, First SDRAM                                                           |                                      |                             |          |

|      | DRAM Refresh Management, First Byte, First SURAM<br>DRAM Refresh Management, Second Byte, First SDRAM      | +                                    |                             |          |

| _    | URAM Refresh Management, Second Byte, First SURAM<br>DRAM Refresh Management, First Byte, Second SDRAM     | +                                    |                             |          |

| -    | URAM Remesh Management, First Byte, Second SURAM<br>DRAM Refresh Management, Second Byte, Second SDRAM     |                                      |                             |          |

| _    |                                                                                                            |                                      |                             |          |

| N 18 | DRAM Adaptive Refresh Management, First SDRAM, First Byte,Level A                                          |                                      |                             | _        |

| _    | DRAM Adaptive Refresh Management, First SDRAM, Second Byte, Level A                                        |                                      |                             |          |

| 61                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, Second SDRAM, Second Byte,Level A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                         | <b>r</b> 00 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|

|                                                                                                                                                                                                                | SDRAM Adaptive Refresh Management, First SDRAM, First Byte Level B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                         | 00          |

| 63                                                                                                                                                                                                             | SDRAM Adaptive Retresh Management, First SDRAM, Second Byte,Level B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                         | 00          |

| 64                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, Second SDRAM, First Byte,Level B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                         | 00          |

| 65                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, Second SDRAM, Second Byte,Level B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                         | 00          |

| 66                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, First SDRAM, First Byte,Level C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                         | 00          |

| 67                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, First SDRAM, Second Byte,Level C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                         | 00          |

| 68                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, Second SDRAM, First Byte,Level C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                         | 00          |

| 69                                                                                                                                                                                                             | SDRAM Adaptive Refresh Management, Second SDRAM, Second Byte,Level C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                         | 00          |

| 70                                                                                                                                                                                                             | SDRAM Minimum Active to Active Command Delay Time, Same Bank Group,(IRRD Lmin),Least Significant Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5000 ps                                                                 | 8           |

| 71                                                                                                                                                                                                             | SDRAM Minimum Active to Active Command Delay Time, Same Bank Group,(IRRD Lmin),Most Significant Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000 pa                                                                 | 18          |

| 72                                                                                                                                                                                                             | SDRAM Minimum Active to Active Command Delay Time, Same Bank Group,(IRRD Lmin),Lower Clock Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 nCK                                                                   | 00          |

|                                                                                                                                                                                                                | SDRAM Minimum CAS in to CAS in Command Delay Time, Same Bank Group,(ICCD Lmin),Least Significant Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5000 ps                                                                 | 8           |

| 74                                                                                                                                                                                                             | SDRAM Minimum CAS in to CAS in Command Delay Time, Same Bank Group,(tCCD Lmin),Most Significant Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                         | 1           |

|                                                                                                                                                                                                                | SDRAM Minimum CAS in to CAS in Command Delay Time, Same Bank Group,(ICCD Lmin),Lower Clock Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 nCK                                                                   | 00          |